What Is Bus Interface A computer employs RAM chips of 1024 x 8 and ROM chips of 2048 x 4 The computer system needs 2K bytes of RAM and 2K bytes of ROM and an interface unit with 256 registers each A memory mapped I O configuration is used The two higher order bits of the address bus are assigned 00 for RAM 01

Hi I am trying to design a system where I have to communicate two nodes using CAN or RS485 which are powered from isolated supplies The node grounds cannot be tied together Supposing I don t use isolated transceivers is it okay to only transmit using the two differential wires of the I am trying to understand how many I2C devices can be connected on one I2C bus for 8bit 16bit 32bits microcontroller how it decides how many devices can be connected I found that a total of 128 devices can be connected to the bus if the device address is 7 bits

What Is Bus Interface

What Is Bus Interface

https://thecheesewanker.com/wp-content/uploads/2023/06/What-Does-Gruyere-Taste-Like-6.jpg

Referentes En Cambio Clim tico Y Transici n Ecol gica Eurecat

https://eurecat.org/wp-content/uploads/2023/03/2019FORUMTURISTIC378_retall.jpg

Decoding The Net Promoter Score Its Significance And Calculation Blog

https://www.novelvox.com/wp-content/uploads/2024/04/What-is-Net-Promoter-Score.jpg

But as a contingency plan I d like to have more margin from failure and my thought was to go to CAN bus I was hoping there was a transceiver out there that would take I2C and output CAN But I haven t found it Any suggestions of part numbers or a different approach to interface I2C sensors with a pi zero at 10ft ultra reliably Thanks Seeing that can bus has j spec for its protocol s I thought maybe it wouldn t be as bad to decode since there is standards towards how obd and j specs are done Maybe I am wrong Your servo comment peaked my interest after some thought The controller currently in the truck use s a can bus However it has a arm that moves the vanes in the turbo

The FPGA does not have an I2C interface just logic pins Its only the chips with processors in that have native I2C interfaces A standard Schmitt trigger will not remove or prevent the I2C glitch that can happen on any I2C bus especially one with multiple masters The I2C glitch is just to slow and to big for a silicon Schmitt to do anything apart form pass the I2c interface voltage input low level digital zero 0 6V maximum i2c interface voltage input high level digital 1 iovdd 0 5 the iovdd maximum is 3 5V therefore iovdd 0 5 3 5 0 5 4V maximum If you use 19V for the bus you will damage destroy the sda and scl circuits that are in the ic

More picture related to What Is Bus Interface

What City Hosted This Year s Winter Olympics Free Beer And Hot Wings

https://www.freebeerandhotwings.com/wp-content/uploads/2022/12/What-City-Hosted-This-Years-Winter-Olympics.jpg

Skechers Hands Free Slip Ins GO Walk 7 Easy On 2 Slip On Sneaker Men

https://images.dsw.com/is/image/DSWShoes/578460_011_ss_01

What Actress Married Tom Cruise On Christmas Eve In 1990 Free Beer

https://www.freebeerandhotwings.com/wp-content/uploads/2022/12/What-Actress-Married-Tom-Cruise-On-Christmas-Eve-In-1990.jpg

CANBus is a differential bus At the idling or recessive state both CANH and CANL sit at 2 5 volts During the dominant state CANH gets pulled to aprox 5 volts and CANL to aprox zero volts But as Ian has mentioned it can tolerate a lot of common mode voltage mismatch QUESTION FOR YOU did you employ the 120 ohm termination resistor Can anyone suggest a microcontroller with 2 SPI buses units need to connect to 2 peripherals over SPI I think having two seperate units will be a lot easier and 1 CAN Bus any suggestions would be warmly welcome if anyone knows any under TI or NXP LPC that would be a bonus wanted to gauge peoples opinions first any help would be greatly appreciated

[desc-10] [desc-11]

What Band Had Hits With Push 3 AM And More Free Beer And Hot Wings

https://www.freebeerandhotwings.com/wp-content/uploads/2022/11/What-Band-Had-Hits-With-Push-3-AM-And-More.jpg

What Did Saint Patrick Use To Explain The Holy Trinity Free Beer And

https://www.freebeerandhotwings.com/wp-content/uploads/2022/11/What-Did-Saint-Patrick-Use-To-Explain-The-Holy-Trinity.jpg

https://forum.allaboutcircuits.com › threads

A computer employs RAM chips of 1024 x 8 and ROM chips of 2048 x 4 The computer system needs 2K bytes of RAM and 2K bytes of ROM and an interface unit with 256 registers each A memory mapped I O configuration is used The two higher order bits of the address bus are assigned 00 for RAM 01

https://forum.allaboutcircuits.com › threads

Hi I am trying to design a system where I have to communicate two nodes using CAN or RS485 which are powered from isolated supplies The node grounds cannot be tied together Supposing I don t use isolated transceivers is it okay to only transmit using the two differential wires of the

Learn How The CAN Bus Works Controller Area Network Embedded

What Band Had Hits With Push 3 AM And More Free Beer And Hot Wings

8086 Registers Of Bus Interface Unit YouTube

What Is Bus Interface Unit BIU In 8086 Microprocessor Ekeeda

Telestia Terra Esfort Tensei Kizoku No Isekai Bouken Roku Image By

Engram

Engram

Yankely Menendez Instagram

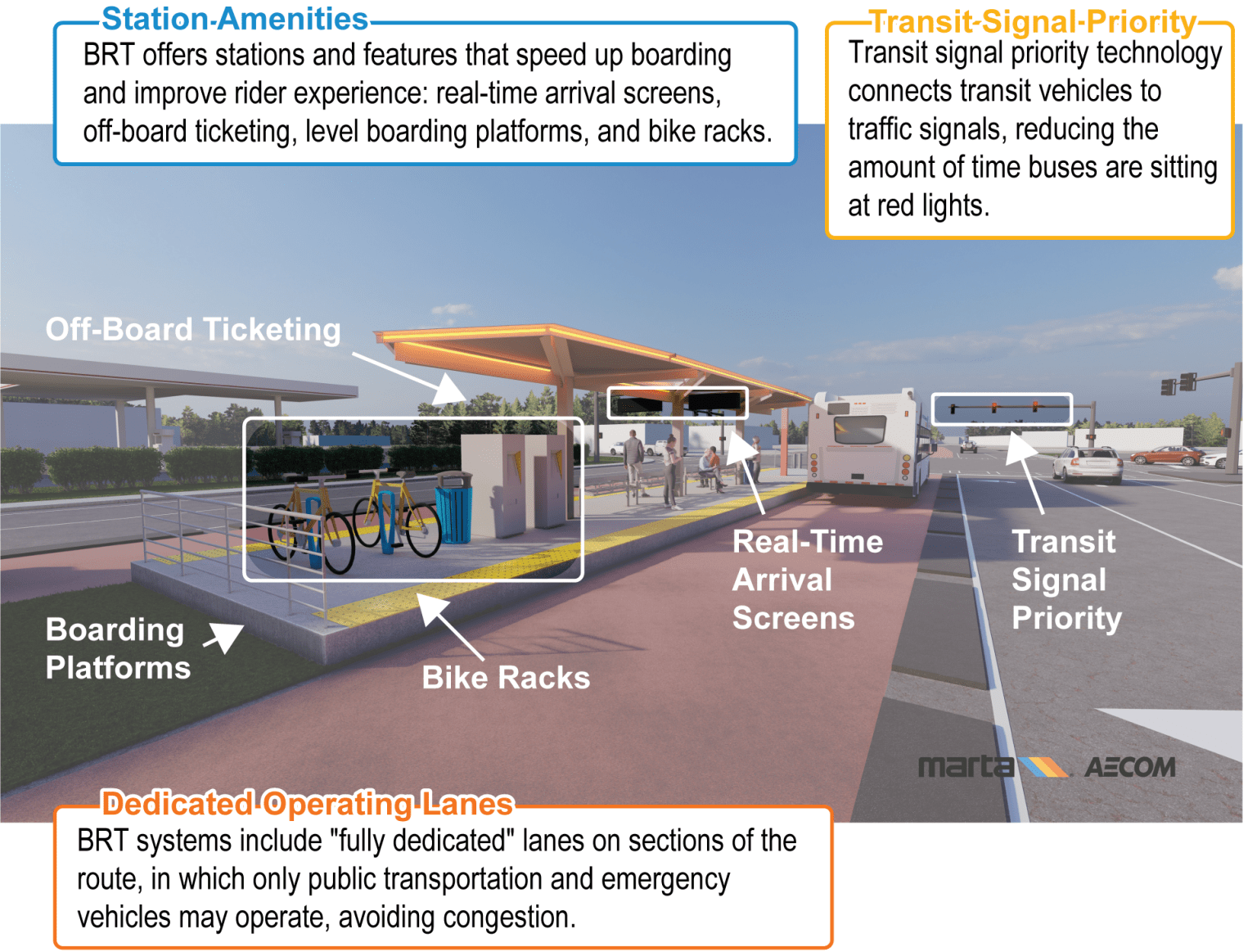

What Is BRT Connect Clayton

What Is AS Interface RealPars

What Is Bus Interface - The FPGA does not have an I2C interface just logic pins Its only the chips with processors in that have native I2C interfaces A standard Schmitt trigger will not remove or prevent the I2C glitch that can happen on any I2C bus especially one with multiple masters The I2C glitch is just to slow and to big for a silicon Schmitt to do anything apart form pass the